Edition 1.0 2015-03

### INTERNATIONAL IEEE Std 1801™-2013 STANDARD

**Design and Verification of Low-Power Integrated Circuits**

INTERNATIONAL ELECTROTECHNICAL COMMISSION

ICS 25.040; 35.060 ISBN 978-2-8322-2266-9

Warning! Make sure that you obtained this publication from an authorized distributor.

#### **Contents**

| 1. | Over                                     | view                                            | 1  |

|----|------------------------------------------|-------------------------------------------------|----|

|    | 1.1                                      | Scope                                           | 1  |

|    | 1.2                                      | Purpose                                         |    |

|    | 1.3                                      | Key characteristics of the Unified Power Format |    |

|    | 1.4                                      | Use of color in this standard                   |    |

|    | 1.5                                      | Contents of this standard                       | 3  |

| 2. | Norn                                     | native references                               | 4  |

| 3. | Definitions, acronyms, and abbreviations |                                                 |    |

|    | 3.1                                      | Definitions                                     | 4  |

|    | 3.2                                      | Acronyms and abbreviations                      |    |

| 4. | UPF concepts                             |                                                 | 11 |

|    | 4.1                                      | Design structure                                | 11 |

|    | 4.2                                      | Design representation                           |    |

|    | 4.3                                      | Power architecture                              |    |

|    | 4.4                                      | Power distribution                              |    |

|    | 4.5                                      | Power management                                |    |

|    | 4.6                                      | Power states                                    |    |

|    | 4.7                                      | Simstates                                       |    |

|    | 4.8                                      | Successive refinement.                          |    |

|    | 4.9                                      | Tool flow                                       |    |

|    |                                          | File structure                                  |    |

| 5. | Language basics                          |                                                 | 33 |

|    | 5.1                                      | UPF is Tcl                                      | 33 |

|    | 5.2                                      | Conventions used                                |    |

|    | 5.3                                      | Lexical elements                                |    |

|    | 5.4                                      | Boolean expressions                             |    |

|    | 5.5                                      | Object declaration                              |    |

|    | 5.6                                      | Attributes of objects                           |    |

|    | 5.7                                      | Power state name spaces                         |    |

|    | 5.8                                      | Precedence                                      |    |

|    | 5.9                                      | Generic UPF command semantics                   |    |

|    |                                          | effective_element_list semantics                |    |

|    | 5.11                                     |                                                 |    |

|    |                                          | Error handling                                  |    |

|    |                                          | Units                                           |    |

| 6. | Power intent commands                    |                                                 | 51 |

|    | 6.1                                      | Categories                                      | 51 |

|    | 6.2                                      | add domain elements [deprecated]                |    |

|    | 6.3                                      | add port state [legacy]                         |    |

|    | 6.4                                      | add power state                                 |    |

|    | 6.5                                      | add pst state [legacy]                          |    |

|    | 6.6                                      | apply power model                               |    |

|    | 6.7                                      | associate supply set                            |    |

|    |                                          | _ 11 /_                                         |    |

7.

| 6.8  | begin_power_model                   |      |  |  |  |

|------|-------------------------------------|------|--|--|--|

| 6.9  | bind_checker                        |      |  |  |  |

| 6.10 | connect_logic_net                   | . 63 |  |  |  |

| 6.11 | connect_supply_net                  |      |  |  |  |

| 6.12 | connect_supply_set                  |      |  |  |  |

| 6.13 | create_composite_domain             | . 67 |  |  |  |

| 6.14 | create_hdl2upf_vct                  | . 68 |  |  |  |

| 6.15 | create_logic_net                    | . 69 |  |  |  |

| 6.16 | create_logic_port                   |      |  |  |  |

| 6.17 | create_power_domain                 | . 71 |  |  |  |

| 6.18 | create_power_switch                 | . 74 |  |  |  |

| 6.19 | create_pst [legacy]                 | . 80 |  |  |  |

| 6.20 | create_supply_net                   |      |  |  |  |

| 6.21 | create_supply_port                  |      |  |  |  |

| 6.22 | create_supply_set                   |      |  |  |  |

| 6.23 | create_upf2hdl_vct                  |      |  |  |  |

|      | describe_state_transition           |      |  |  |  |

|      | end_power_model                     |      |  |  |  |

| 6.26 | find_objects                        |      |  |  |  |

| 6.27 | <del>-</del> -                      |      |  |  |  |

|      | load_upf                            |      |  |  |  |

| 6.29 | load_upf_protected                  |      |  |  |  |

| 6.30 |                                     |      |  |  |  |

| 6.31 | map_level_shifter_cell [deprecated] |      |  |  |  |

|      | map_power_switch                    |      |  |  |  |

| 6.33 | map_retention_cell                  |      |  |  |  |

| 6.34 | merge_power_domains [deprecated]    |      |  |  |  |

| 6.35 | name_format                         |      |  |  |  |

| 6.36 | save_upf                            |      |  |  |  |

| 6.37 | set_design_attributes               |      |  |  |  |

| 6.38 | set_design_top                      |      |  |  |  |

| 6.39 | set_domain_supply_net [legacy]      |      |  |  |  |

| 6.40 | set_equivalent                      |      |  |  |  |

| 6.41 | set_isolation                       |      |  |  |  |

| 6.42 | set_isolation_control [deprecated]  |      |  |  |  |

| 6.43 | set_level_shifter                   |      |  |  |  |

|      | set_partial_on_translation          |      |  |  |  |

| 6.45 | set_pin_related_supply [deprecated] |      |  |  |  |

| 6.46 | set_port_attributes                 |      |  |  |  |

| 6.47 | set_power_switch [deprecated]       |      |  |  |  |

| 6.48 | <u> </u>                            |      |  |  |  |

|      | set_retention                       |      |  |  |  |

| 6.50 | : : :                               |      |  |  |  |

| 6.51 | set_retention_elements              |      |  |  |  |

| 6.52 | set_scope                           |      |  |  |  |

| 6.53 | set_simstate_behavior               |      |  |  |  |

| 6.54 | upf_version                         |      |  |  |  |

| 0.33 | use_interface_cell                  | 132  |  |  |  |

| Powe | Power management cell commands      |      |  |  |  |

| 7.1  | Introduction                        | 135  |  |  |  |

| 7.2  | define always on cell.              |      |  |  |  |

| 7.3  | _ ,                                 | 137  |  |  |  |

|      | 7.4     | define_isolation_cell                                                  | 138 |

|------|---------|------------------------------------------------------------------------|-----|

|      | 7.5     | define_level_shifter_cell                                              | 141 |

|      | 7.6     | define_power_switch_cell                                               | 145 |

|      | 7.7     | define_retention_cell                                                  | 147 |

| 8.   | UPF     | processing                                                             | 150 |

|      | 8.1     | Overview                                                               | 150 |

|      | 8.2     | Data requirements                                                      | 150 |

|      | 8.3     | Processing phases                                                      |     |

|      | 8.4     | Error checking                                                         | 153 |

| 9.   | Sim     | ulation semantics                                                      | 154 |

|      | 9.1     | Supply network creation                                                | 154 |

|      | 9.2     | Supply network simulation                                              |     |

|      | 9.3     | Power state simulation                                                 |     |

|      | 9.4     | Simstate simulation                                                    |     |

|      | 9.5     | Transitioning from one simstate state to another                       |     |

|      | 9.6     | Simulation of retention                                                |     |

|      | 9.7     | Simulation of isolation                                                |     |

|      | 9.8     | Simulation of level-shifting                                           |     |

|      | 9.9     | Simulation of repeater                                                 | 168 |

| Anne | x A (ii | nformative) Bibliography                                               | 169 |

| Anne | х В (n  | ormative) HDL package UPF                                              | 170 |

| Anne | x C (n  | ormative) Queries                                                      | 182 |

| Anne | x D (iı | nformative) Replacing deprecated and legacy commands and options       | 219 |

| Anne | x E (ir | formative) Low-power design methodology                                | 227 |

| Anne | x F (no | ormative) Value conversion tables                                      | 252 |

| Anne | x G (n  | ormative) Supporting hard IP                                           | 255 |

| Anne | х H (n  | ormative) UPF power-management commands semantics and Liberty mappings | 258 |

| Anne | x I (in | formative) Power-management cell modeling examples                     | 273 |

| Anne | x J (in | formative) Switching Activity Interchange Format                       | 303 |

| Anne | x K(in  | formative) IEEE List of Participants                                   | 333 |

## DESIGN AND VERIFICATION OF LOW-POWER INTEGRATED CIRCUITS

#### **FOREWORD**

1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as "IEC Publication(s)"). Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and non-governmental organizations liaising with the IEC also participate in this preparation.

IEEE Standards documents are developed within IEEE Societies and Standards Coordinating Committees of the IEEE Standards Association (IEEE-SA) Standards Board. IEEE develops its standards through a consensus development process, which brings together volunteers representing varied viewpoints and interests to achieve the final product. Volunteers are not necessarily members of IEEE and serve without compensation. While IEEE administers the process and establishes rules to promote fairness in the consensus development process, IEEE does not independently evaluate, test, or verify the accuracy of any of the information contained in its standards. Use of IEEE Standards documents is wholly voluntary. IEEE documents are made available for use subject to important notices and legal disclaimers (see <a href="https://standards.ieee.org/IPR/disclaimers.html">https://standards.ieee.org/IPR/disclaimers.html</a> for more information).

IEC collaborates closely with IEEE in accordance with conditions determined by agreement between the two organizations.

- 2) The formal decisions of IEC on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested IEC National Committees. The formal decisions of IEEE on technical matters, once consensus within IEEE Societies and Standards Coordinating Committees has been reached, is determined by a balanced ballot of materially interested parties who indicate interest in reviewing the proposed standard. Final approval of the IEEE standards document is given by the IEEE Standards Association (IEEE-SA) Standards Board.

- 3) IEC/IEEE Publications have the form of recommendations for international use and are accepted by IEC National Committees/IEEE Societies in that sense. While all reasonable efforts are made to ensure that the technical content of IEC/IEEE Publications is accurate, IEC or IEEE cannot be held responsible for the way in which they are used or for any misinterpretation by any end user.

- 4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications (including IEC/IEEE Publications) transparently to the maximum extent possible in their national and regional publications. Any divergence between any IEC/IEEE Publication and the corresponding national or regional publication shall be clearly indicated in the latter.

- 5) IEC and IEEE do not provide any attestation of conformity. Independent certification bodies provide conformity assessment services and, in some areas, access to IEC marks of conformity. IEC and IEEE are not responsible for any services carried out by independent certification bodies.

- 6) All users should ensure that they have the latest edition of this publication.

- 7) No liability shall attach to IEC or IEEE or their directors, employees, servants or agents including individual experts and members of technical committees and IEC National Committees, or volunteers of IEEE Societies and the Standards Coordinating Committees of the IEEE Standards Association (IEEE-SA) Standards Board, for any personal injury, property damage or other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and expenses arising out of the publication, use of, or reliance upon, this IEC/IEEE Publication or any other IEC or IEEE Publications.

- 8) Attention is drawn to the normative references cited in this publication. Use of the referenced publications is indispensable for the correct application of this publication.

- 9) Attention is drawn to the possibility that implementation of this IEC/IEEE Publication may require use of material covered by patent rights. By publication of this standard, no position is taken with respect to the existence or validity of any patent rights in connection therewith. IEC or IEEE shall not be held responsible for identifying Essential Patent Claims for which a license may be required, for conducting inquiries into the legal validity or scope of Patent Claims or determining whether any licensing terms or conditions provided in connection with submission of a Letter of Assurance, if any, or in any licensing agreements are reasonable or non-discriminatory. Users of this standard are expressly advised that determination of the validity of any patent rights, and the risk of infringement of such rights, is entirely their own responsibility.

International Standard IEC 61523-4/IEEE Std 1801-2013 has been processed through IEC technical committee 91: Electronics assembly technology, under the IEC/IEEE Dual Logo Agreement.

The text of this standard is based on the following documents:

| IEEE Std    | FDIS         | Report on voting |  |

|-------------|--------------|------------------|--|

| 1801 (2013) | 91/1209/FDIS | 91/1228/RVD      |  |

Full information on the voting for the approval of this standard can be found in the report on voting indicated in the above table.

The IEC Technical Committee and IEEE Technical Committee have decided that the contents of this publication will remain unchanged until the stability date indicated on the IEC web site under "http://webstore.iec.ch" in the data related to the specific publication. At this date, the publication will be

- reconfirmed,

- withdrawn,

- · replaced by a revised edition, or

- · amended.

IEEE Std 1801™-2013 (Revision of IEEE Std 1801-2009)

# IEEE Standard for Design and Verification of Low-Power Integrated Circuits

Sponsor

Design Automation Committee

of the

IEEE Computer Society

and the

IEEE Standards Association Corporate Advisory Group

Approved 6 March 2013

**IEEE-SA Standards Board**

Grateful acknowledgment is made to the following for permission to use source material:

Accellera Systems Initiative

Unified Power Format (UPF) Standard, Version 1.0

Cadence Design Systems, Inc.

Library Cell Modeling Guide Using CPF Hierarchical Power Intent Modeling Guide Using CPF

Silicon Integration Initiative, Inc.

Si2 Common Power Format Specification, Version 2.0

**Abstract:** A method is provided for specifying power intent for an electronic design, for use in verification of the structure and behavior of the design in the context of a given power management architecture, and for driving implementation of that power management architecture. The method supports incremental refinement of power intent specifications required for IP-based design flows. **Keywords:** corruption semantics, IEEE 1801™, interface specification, IP reuse, isolation, level-shifting, power-aware design, power domains, power intent, power modes, power states, progressive design refinement, retention, retention strategies

Verilog is a registered trademark of Cadence Design Systems, Inc.

#### **IEEE Introduction**

This introduction is not part of IEEE Std 1801-2013, IEEE Standard for Design and Verification of Low-Power Integrated Circuits.

The purpose of this standard is to provide portable low-power design specifications that can be used with a variety of commercial products throughout an electronic system design, analysis, verification, and implementation flow.

When the electronic design automation (EDA) industry began creating standards for use in specifying, simulating, and implementing functional specifications of digital electronic circuits in the 1980s, the primary design constraint was the transistor area necessary to implement the required functionality in the prevailing process technology at that time. Power considerations were simple and easily assumed for the design as power consumption was not a major consideration and most chips operated on a single voltage for all functionality. Therefore, hardware description languages (HDLs) such as VHDL (IEC 61691-1-1/ IEEE Std 1076<sup>TM</sup>)<sup>a</sup> and SystemVerilog (IEEE Std 1800<sup>TM</sup>) provided a rich set of capabilities necessary for capturing the functional specification of electronic systems, but no capabilities for capturing the power architecture (how each element of the system is to be powered).

As the process technology for manufacturing electronic circuits continued to advance, power (as a design constraint) continually increased in importance. Even above the 90 nm process node size, dynamic power consumption became an important design constraint as the functional size of designs increased power consumption at the same time battery-operated mobile systems, such as cell phones and laptop computers, became a significant driver of the electronics industry. Techniques for reducing dynamic power consumption—the amount of power consumed to transition a node from a 0 to 1 state or vice versa—became commonplace. Although these techniques affected the design methodology, the changes were relatively easy to accommodate within the existing HDL-based design flow, as these techniques were primarily focused on managing the clocking for the design (more clock domains operating at different frequencies and gating of clocks when logic in a clock domain is not needed for the active operational mode). Multi-voltage power-management methods were also developed. These methods did not directly impact the functionality of the design, requiring only level-shifters between different voltage domains. Multi-voltage power domains could be verified in existing design flows with additional, straight-forward extensions to the methodology.

With process technologies below 100 nm, static power consumption has become a prominent and, in many cases, dominant design constraint. Due to the physics of the smaller process nodes, power is leaked from transistors even when the circuitry is quiescent (no toggling of nodes from 0 to 1 or vice versa). New design techniques were developed to manage static power consumption. Power gating or power shut-off turns off power for a set of logic elements. Back-bias techniques are used to raise the voltage threshold at which a transistor can change its state. While back bias slows the performance of the transistor, it greatly reduces leakage. These techniques are often combined with multi-voltages and require additional functionality: power-management controllers, isolation cells that logically and/or electrically isolate a shutdown power domain from "powered-up" domains, level-shifters that translate signal voltages from one domain to another, and retention registers to facilitate fast transition from a power-off state to a power-on state for a domain.

The EDA industry responded with multiple vendors developing proprietary low-power specification capabilities for different tools in the design and implementation flow. Although this solved the problem locally for a given tool, it was not a global solution in that the same information was often required to be specified multiple times for different tools without portability of the power specification. At the Design

<sup>&</sup>lt;sup>a</sup>Information on references can be found in Clause 2.

Automation Conference (DAC) in June 2006, several semiconductor/electronics companies challenged the EDA industry to define an open, portable power specification standard. The EDA industry standards incubation consortium, Accellera Systems Initiative, answered the call by creating a Technical SubCommittee (TSC) to develop a standard. The effort was named Unified Power Format (UPF) to recognize the need of unifying the capabilities of multiple proprietary formats into a single industry standard. Accellera approved *UPF 1.0* as an Accellera standard in February 2007. In May 2007, Accellera donated UPF to the IEEE for the purposes of creating an IEEE standard, and in March 2009, the first version of the IEEE Std 1801 was released. So this standard, although the second version of the IEEE Std 1801, represents the third version of what is more colloquially referred to as UPF.

#### **Notice to users**

#### Laws and regulations

Users of IEEE Standards documents should consult all applicable laws and regulations. Compliance with the provisions of any IEEE Standards document does not imply compliance to any applicable regulatory requirements. Implementers of the standard are responsible for observing or referring to the applicable regulatory requirements. IEEE does not, by the publication of its standards, intend to urge action that is not in compliance with applicable laws, and these documents may not be construed as doing so.

#### Copyrights

This document is copyrighted by the IEEE. It is made available for a wide variety of both public and private uses. These include both use, by reference, in laws and regulations, and use in private self-regulation, standardization, and the promotion of engineering practices and methods. By making this document available for use and adoption by public authorities and private users, the IEEE does not waive any rights in copyright to this document.

#### **Updating of IEEE documents**

Users of IEEE Standards documents should be aware that these documents may be superseded at any time by the issuance of new editions or may be amended from time to time through the issuance of amendments, corrigenda, or errata. An official IEEE document at any point in time consists of the current edition of the document together with any amendments, corrigenda, or errata then in effect. In order to determine whether a given document is the current edition and whether it has been amended through the issuance of amendments, corrigenda, or errata, visit the IEEE-SA Website at <a href="http://standards.ieee.org/index.html">http://standards.ieee.org/index.html</a> or contact the IEEE at the address listed previously. For more information about the IEEE Standards Association or the IEEE standards development process, visit IEEE-SA Website at <a href="http://standards.ieee.org/index.html">http://standards.ieee.org/index.html</a>.

#### **Errata**

Errata, if any, for this and all other standards can be accessed at the following URL: <a href="http://standards.ieee.org/findstds/errata/index.html">http://standards.ieee.org/findstds/errata/index.html</a>. Users are encouraged to check this URL for errata periodically.

#### **Patents**

Attention is called to the possibility that implementation of this standard may require use of subject matter covered by patent rights. By publication of this standard, no position is taken by the IEEE with respect to the existence or validity of any patent rights in connection therewith. If a patent holder or patent applicant has filed a statement of assurance via an Accepted Letter of Assurance, then the statement is listed on the IEEE-SA Website at <a href="http://standards.ieee.org/about/sasb/patcom/patents.html">http://standards.ieee.org/about/sasb/patcom/patents.html</a>. Letters of Assurance may indicate whether the Submitter is willing or unwilling to grant licenses under patent rights without compensation or under reasonable rates, with reasonable terms and conditions that are demonstrably free of any unfair discrimination to applicants desiring to obtain such licenses.

Essential Patent Claims may exist for which a Letter of Assurance has not been received. The IEEE is not responsible for identifying Essential Patent Claims for which a license may be required, for conducting inquiries into the legal validity or scope of Patents Claims, or determining whether any licensing terms or conditions provided in connection with submission of a Letter of Assurance, if any, or in any licensing agreements are reasonable or non-discriminatory. Users of this standard are expressly advised that determination of the validity of any patent rights, and the risk of infringement of such rights, is entirely their own responsibility. Further information may be obtained from the IEEE Standards Association.

## Design and Verification of Low-Power Integrated Circuits

IMPORTANT NOTICE: This standard is not intended to ensure safety, security, health, or environmental protection in all circumstances. Implementers of the standard are responsible for determining appropriate safety, security, environmental, and health practices or regulatory requirements.

This IEEE document is made available for use subject to important notices and legal disclaimers. These notices and disclaimers appear in all publications containing this document and may be found under the heading "Important Notice" or "Important Notices and Disclaimers Concerning IEEE Documents." They can also be obtained on request from IEEE or viewed at <a href="http://standards.ieee.org/IPR/disclaimers.html">http://standards.ieee.org/IPR/disclaimers.html</a>.

#### 1. Overview

#### 1.1 Scope

This standard establishes a format used to define the low-power design intent for electronic systems and electronic intellectual property (IP). The format provides the ability to specify the supply network, switches, isolation, retention, and other aspects relevant to power management of an electronic system. The standard defines the relationship between the low-power design specification and the logic design specification captured via other formats [e.g., standard hardware description languages (HDLs)].

#### 1.2 Purpose

The standard provides portability of low-power design specifications that can be used with a variety of commercial products throughout an electronic system design, analysis, verification, and implementation flow.

#### 1.3 Key characteristics of the Unified Power Format

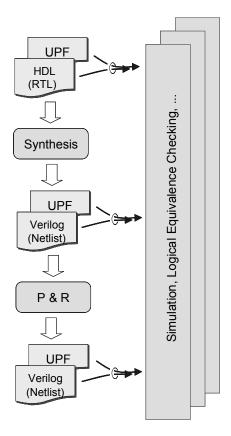

The Unified Power Format (UPF) provides the ability for electronic systems to be designed with power as a key consideration early in the process. UPF accomplishes this by allowing the specification of what was traditionally physical implementation-based power information early in the design process—at the register transfer level (RTL) or earlier. Figure 1 shows UPF supporting the entire design flow. UPF provides a

consistent format to specify power design information that may not be easily specifiable in an HDL or when it is undesirable to directly specify the power semantics in an HDL, as doing so would tie the logic specification directly to a constrained power implementation. UPF specifies a set of HDL attributes and HDL packages to facilitate the expression of power intent in HDL when appropriate (see <u>Table 4</u> and <u>Annex B</u>). UPF also defines consistent semantics across verification and implementation, i.e., what is implemented is the same as what has been verified.

Figure 1—UPF tool flow

As indicated in <u>Figure 1</u>, UPF files are part of the design source and, when combined with the HDL, represent a complete design description: the HDL describing the logical intent and the UPF describing the power intent. Combined with the HDL, the UPF files are used to describe the intent of the designer. This collection of source files is the input to several tools, e.g., simulation tools, synthesis tools, and formal verification tools. UPF supports the successive refinement methodology (see <u>4.8</u>) where power intent information will grow along the design flow to provide needed information for each design stage.

- Simulation tools can read the HDL/UPF design input files and perform RTL power-aware simulation. At this stage, the UPF may only contain abstract models such as power domains and supply sets without the need to create the power and ground network and implementation details.

- Synthesis tools can read the HDL/UPF design input files and produce a netlist. The tool or user may

produce a new UPF fileset that, combined with the netlist, represents a further refined version of

same design.

- In those cases where design object names change, a UPF file with the new names is needed. A UPF-aware logical equivalence checker can read the full design and UPF filesets and perform the checks to ensure power-aware equivalence.

- Place and route tools read both the netlist and the UPF files and produce a physical netlist, potentially including an output UPF file.

UPF is a concise power intent specification capability. Power intent can be easily specified over many elements in the design. A UPF specification can be included with the other deliverables of IP blocks and reused along with the other delivered IP. UPF supports various methodologies through carefully defined semantics, flexibility in specification, and, when needed, defined rational limitations that facilitate automation in verification and implementation (see Annex E).

A *UPF specification* defines how to create a supply network to supply power to each instance, how the individual supply nets behave with respect to one another, and how the logic functionality is extended to support dynamic power switching to these logic instances. By controlling the states and voltages of the supplies provided to the supply network, and by controlling the states of power switches that are part of the supply network, the power management logic of a system can cause each functional region to receive the power required to complete its computational tasks in a timely manner.

#### 1.4 Use of color in this standard

This standard uses a minimal amount of color to enhance readability. The coloring is not essential and does not affect the accuracy of this standard when viewed in pure black and white. The places where color is used are the following:

- Cross references that are hyperlinked to other portions of this standard are shown in <u>underlined-blue</u> <u>text</u> (hyperlinking works when this standard is viewed interactively as a PDF file).

- Syntactic keywords and tokens in the formal language definitions are shown in boldface-red text.

- Command arguments that can be provided incrementally (*layered*) are shown in **boldface-green** text. See also <u>5.11</u>.

- Syntactic keywords and tokens that have been explicitly identified as legacy or deprecated constructs (see <u>6.1</u>) may be shown in **brown text**.

#### 1.5 Contents of this standard

The organization of the remainder of this standard is as follows:

- <u>Clause 2</u> provides references to other applicable standards that are presumed or required for this standard.

- <u>Clause 3</u> defines terms and acronyms used throughout the different specifications contained in this standard.

- Clause 4 describes the basic concepts underlying UPF.

- <u>Clause 5</u> describes the language basics for UPF and its commands.

- <u>Clause 6</u> details the syntax and semantics for each UPF power intent command.

- Clause 7 details the syntax and semantics for each UPF power-management cell command.

- <u>Clause 8</u> defines a reference model for UPF command processing.

- Clause 9 defines simulation semantics for various UPF commands.

- Annexes. Following <u>Clause 9</u> are a series of annexes.

#### 2. Normative references

The following referenced documents are indispensable for the application of this standard (i.e., they must be understood and used, so each referenced document is cited in the text and its relationship to this document is explained). For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments or corrigenda) applies.

IEC 61691-1-1/IEEE Std 1076™, Behavioural languages—Part 1: VHDL Language Reference Manual. 1, 2

IEEE Std 1800<sup>TM</sup>, IEEE Standard for SystemVerilog—Unified Hardware Design, Specification, and Verification Language.<sup>3</sup>

<sup>&</sup>lt;sup>1</sup>IEC publications are available from the International Electrotechnical Commission (http://www.iec.ch/). IEC publications are also available in the United States from the American National Standards Institute (http://www.ansi.org/).

<sup>&</sup>lt;sup>2</sup>IEEE publications are available from The Institute of Electrical and Electronics Engineers (<a href="http://standards.ieee.org/">http://standards.ieee.org/</a>).

<sup>&</sup>lt;sup>3</sup>The IEEE standards or products referred to in this clause are trademarks of The Institute of Electrical and Electronics Engineers, Inc.